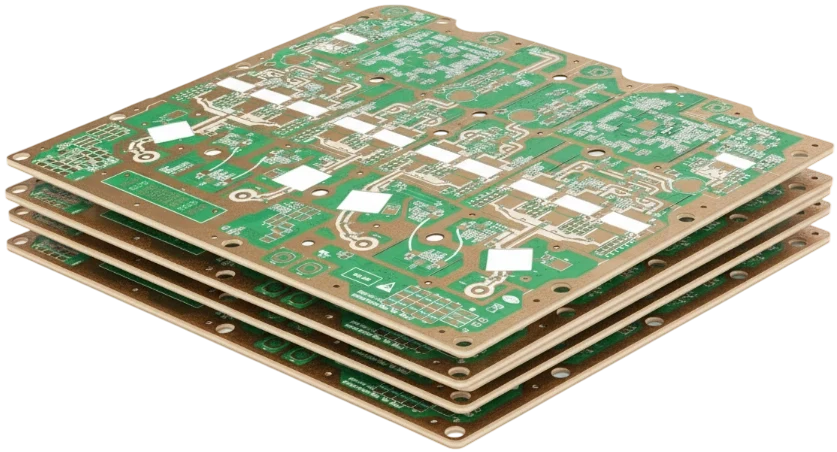

Stackup & CAM

We simulate impedance, copper balance, and lamination sequences before release.

- Confirm materials and acceptable alternates.

- Define sequential lamination plan.

- Plan impedance coupons and reference planes.

- Specify via structures, fill, and backdrill requirements.

- Document finish, coating, and baking instructions.