APTPCB Engineering Whitepaper

Deep Dive: The Physics and Thermodynamics of Advanced PCB Fabrication

For technical architects and lead hardware engineers, standard PCB definitions are inadequate. Understanding the physicochemical realities of the fabrication floor allows engineers to design boards that push the limits of density without sacrificing yield. The following sections provide a rigorous technical breakdown of the critical processes executed at the APTPCB manufacturing facility.

1. Photolithography Limits and LDI Resolution Dynamics

Traditional PCB imaging relies on Mylar film masters and broad-spectrum UV collimated light. This process is fundamentally limited by film expansion (due to temperature/humidity) and light diffraction (undercutting the resist). At APTPCB, we have entirely replaced this with Laser Direct Imaging (LDI). Our LDI systems utilize a 355nm UV laser polygon scanner. The machine reads the fiducials on the actual copper panel and digitally scales the ODB++ image in real-time before firing. This dynamic scaling compensates for the non-linear dimensional changes the FR-4 core experienced during the previous etching steps. This is how we reliably achieve 3-mil (75μm) trace/space resolutions and maintain the strict ±1.0 mil registration required for Any-Layer HDI via-stacking, completely eradicating the risk of annular ring breakout in 0.4mm pitch BGA zones.

2. Fluid Dynamics in High-Aspect-Ratio Copper Plating

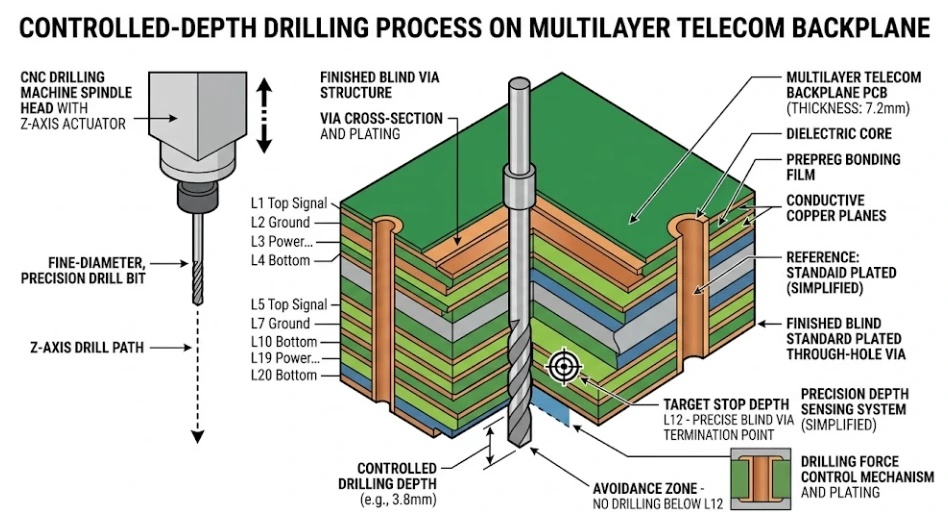

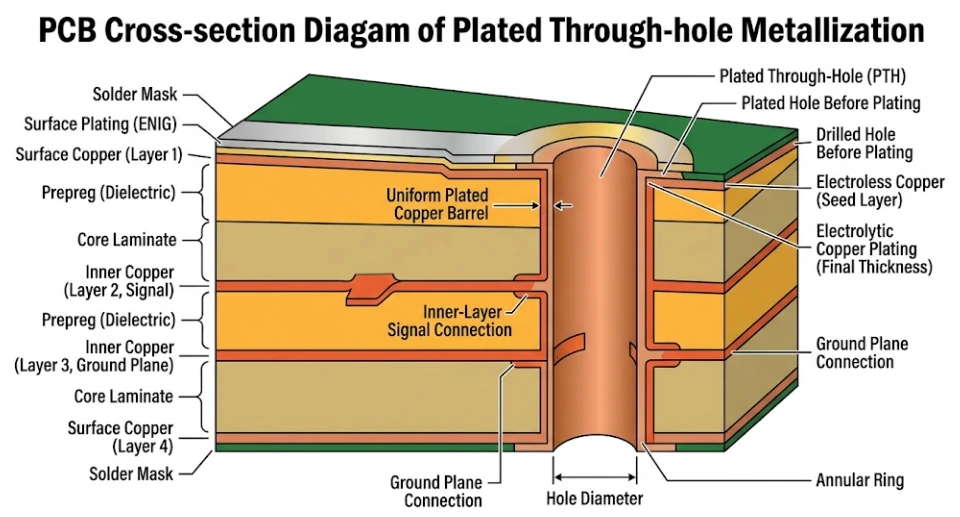

Depositing uniform copper inside a drilled hole is the most critical factor in PCB reliability. The Aspect Ratio (AR) is the board thickness divided by the hole diameter. As board thickness increases (e.g., a 6.0mm telecom backplane) and via sizes shrink (0.3mm), the AR skyrockets to 20:1.

In standard Direct Current (DC) electroplating, the electric field density naturally concentrates at the sharp 90-degree edges of the hole entrance. This causes massive copper buildup at the surface (Dog-Boning) while the center of the via barrel starves for copper ions. The result is a thin, fragile barrel wall that will fracture during the thermal shock of wave soldering.

APTPCB mitigates this via Pulse-Reverse Electroplating. Our rectifiers deliver a millisecond forward pulse (depositing copper), followed instantly by a high-current reverse pulse (anodic stripping). Because the electric field is strongest at the surface, the reverse pulse strips the excess copper from the hole entrance, while leaving the deep-barrel copper intact. By cycling this waveform, we force the plating chemistry deep into the capillary, guaranteeing a uniform 20-25 μm copper barrel thickness from top to bottom, fully compliant with the stringent requirements of IPC-6012 Class 3 / 3A aerospace standards.

3. Resin Rheology and The Lamination Press Cycle

Lamination is not merely melting glue; it is a complex thermosetting polymer reaction. The B-stage prepreg must transition through a liquid phase (minimum melt viscosity) to fill the gaps between etched copper traces, before fully cross-linking into a solid C-stage polymer.

If the heat ramp rate is too fast, the resin polymerizes before the air is fully evacuated, trapping micro-bubbles that will later cause Conductive Anodic Filament (CAF) shorts. If the ramp rate is too slow, the resin flows out to the edges of the panel, leaving the center starved of dielectric (causing fatal impedance drops). APTPCB utilizes vacuum hydraulic presses equipped with dynamic thermal oil heating. Our CAM engineers calculate the exact copper density of your specific design to create a custom pressure/temperature profile. We hold the stack under deep vacuum (to extract volatiles) and precisely manage the rheological flow window, ensuring a void-free, homogenous dielectric matrix even in heavy-copper (3oz+) power electronics boards.

4. Sequential Build-Up (SBU) for Any-Layer HDI

Standard multilayer boards undergo a single lamination cycle. High-Density Interconnect (HDI) smartphones and AI accelerators, however, require Sequential Build-Up (SBU). A 10-layer "Any-Layer ELIC" board is not pressed once; it is built layer-by-layer.

The core is fabricated, drilled, and plated. Then, a layer of dielectric and copper foil is laminated to the outside. A UV laser ablates a microvia down to the core. This via is copper-filled and planarized (VIPPO). Then the next layer is added, and the process repeats. A 3+N+3 structure requires four distinct lamination cycles, four drilling setups, and four plating runs. This exponentially increases manufacturing time and exposes the inner core to multiple high-heat excursions. This is why APTPCB strictly utilizes highly resilient, high-Tg, low-Z-axis-CTE materials (like Isola 370HR or Megtron 6) for all SBU builds, ensuring the foundational vias do not crack during the final pressing cycle.

5. Impedance Metrology and Etch Compensation

Hardware engineers design 50Ω traces based on theoretical geometric models. However, the physical reality of alkaline etching is that traces are not perfect rectangles; they are trapezoids due to the etchant undercutting the photoresist.

To guarantee that your board physically matches your Polar Si9000 simulations, APTPCB performs dynamic Etch-Factor Compensation. If you require a 4.0-mil trace on 1oz copper, our CAM software will image a 4.5-mil trace onto the photoresist. As the panel moves through the etcher, the 0.5-mil undercut reduces the trace to exactly 4.0 mils at its base. Furthermore, we account for the fact that lamination pressure will press the prepreg resin into the adjacent copper gaps, altering the final dielectric thickness (H). By meticulously controlling these physical variables, we routinely hit ±5% impedance tolerances for PCIe Gen 5 and 112G Ethernet protocols, validated by Time Domain Reflectometry (TDR) prior to shipment.