High-Speed CAM & SI Coordination

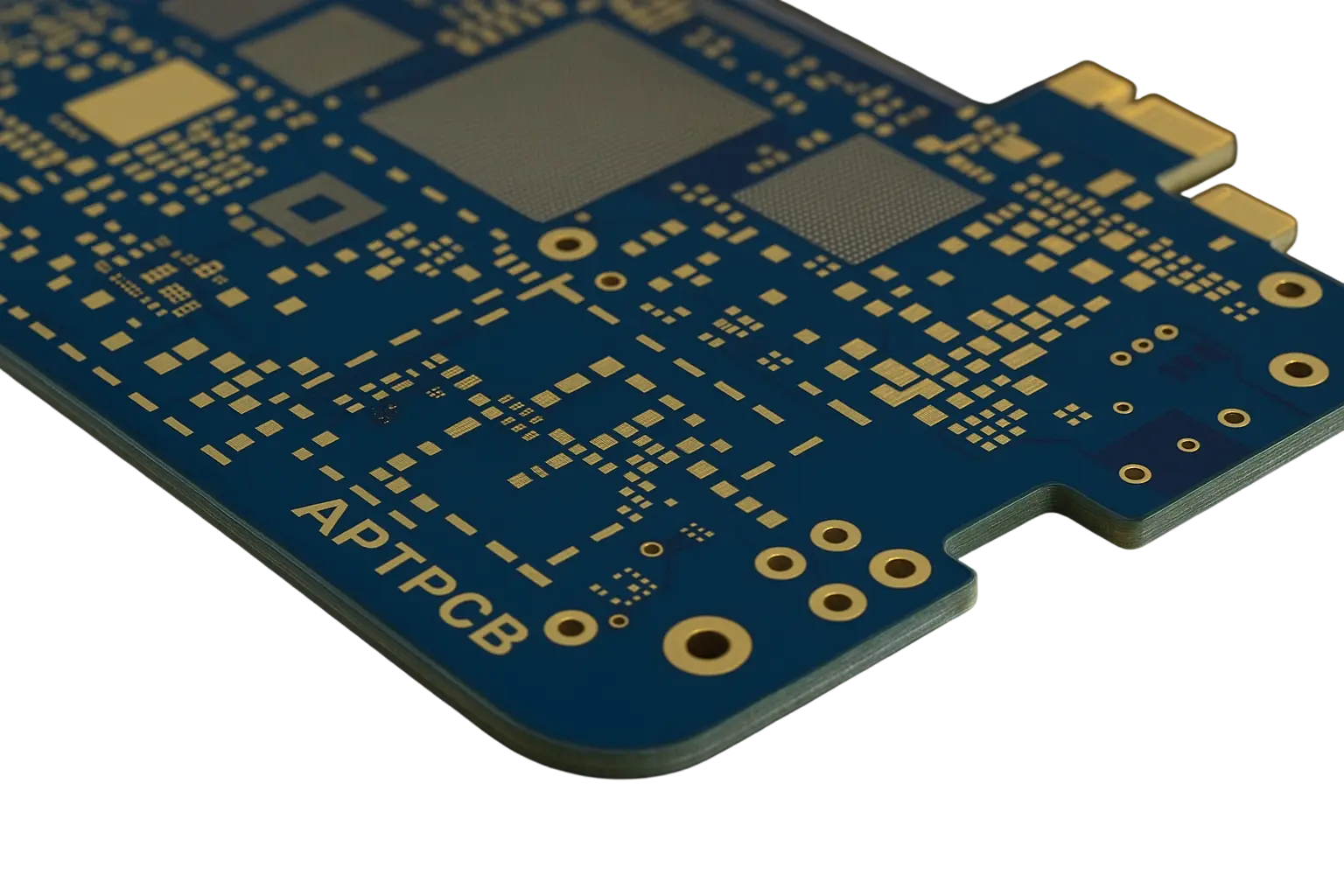

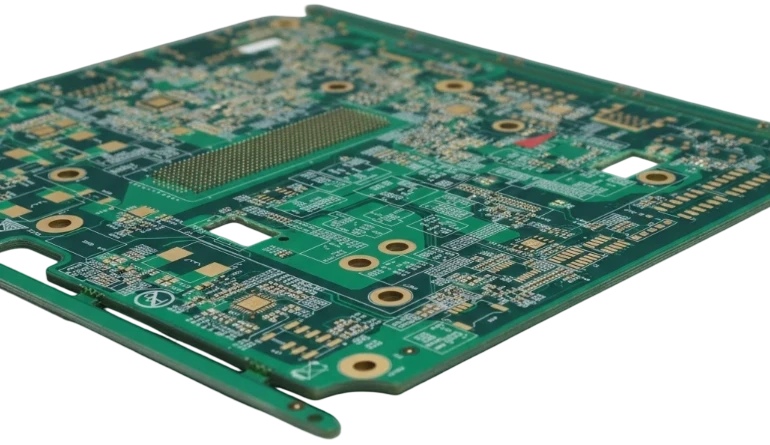

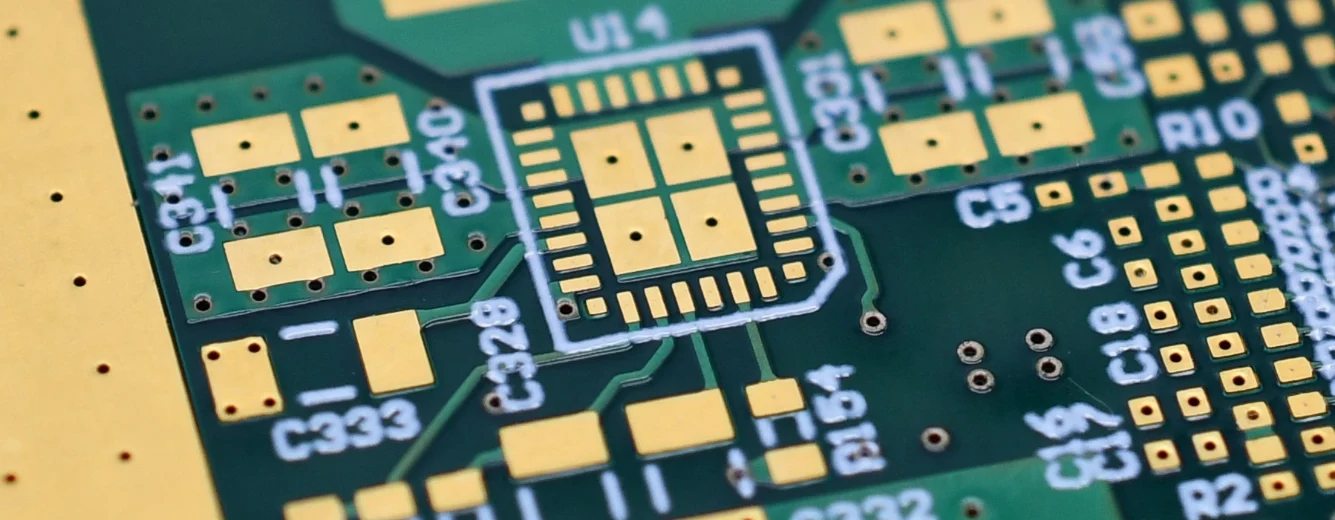

CAM engineers translate SI constraints into manufacturing files, defining stackups, drill maps, impedance coupons, and backdrill coordinates.

- Document dielectric targets, copper roughness, and resin content per layer.

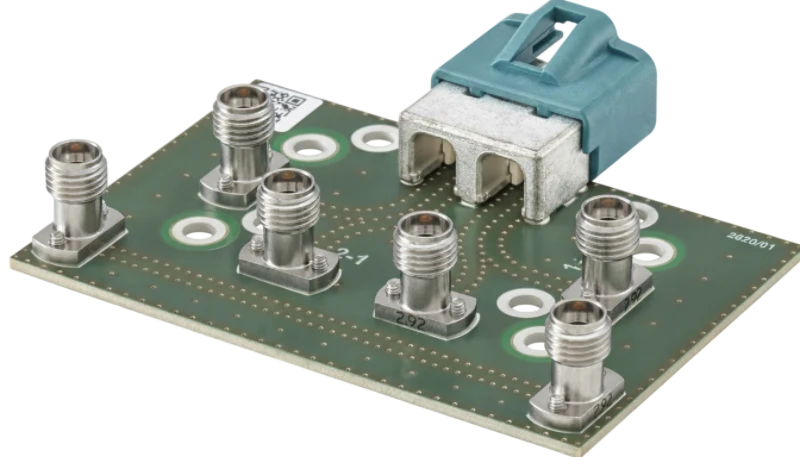

- Define impedance coupons, differential pair geometries, and tolerance stackups.

- Plan backdrill depths, VIPPO fills, and reference plane stitching vias.

- Coordinate press-fit connector footprints and tear-drop requirements.

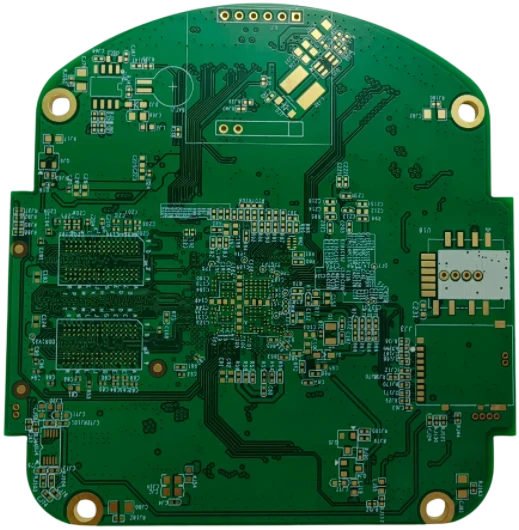

- Simulate or validate via transitions with SI tool outputs.

- Provide handling and baking instructions for low-loss materials.

- Release fabrication notes detailing allowed substitutions and QC checkpoints.