Advanced Engineering Guide

The Engineering Fundamentals of Multilayer PCB Lamination

Designing a multilayer stack-up in software is essentially drawing a theoretical map. However, physically bonding 24 layers of fiberglass, resin, and copper into a single, monolithic, dimensionally stable block is an exercise in applied thermodynamics and materials science. At APTPCB, we partner with hardware engineers globally to demystify the lamination process, ensuring that theoretical designs are highly manufacturable. Below is a deep dive into the engineering strategies governing advanced lamination.

1. Understanding Prepreg Dynamics and Resin Flow

The "glue" holding a multilayer PCB together is Prepreg (pre-impregnated glass cloth). Prepreg consists of woven fiberglass infused with partially cured epoxy resin (known as B-stage). During the lamination press cycle, the application of heat (typically 170°C to 220°C depending on the Tg of the material) causes this B-stage resin to briefly transition into a low-viscosity liquid. Under hydraulic pressure, this liquid resin flows out, filling the etched gaps between the copper traces on the adjacent core layers. As the heat cycle continues, the resin cross-links and permanently hardens into C-stage.

The Engineering Challenge: If you have a layer with 2 oz copper and sparse routing (e.g., just a few traces), there is a massive volume of "empty space" that the resin must fill. If the prepreg selected does not have a high enough Resin Content (RC%) or sufficient flow characteristics, the gaps will not fill. This results in "Resin Starvation"—microscopic air voids that compromise dielectric strength and lead to delamination during assembly. Our CAM engineers mathematically calculate the copper retention percentage of every single layer and intentionally specify specific prepreg glass styles (such as a high-resin 1080 or 106 weave) to guarantee complete, void-free encapsulation.

2. Sequential Lamination for HDI (High-Density Interconnect)

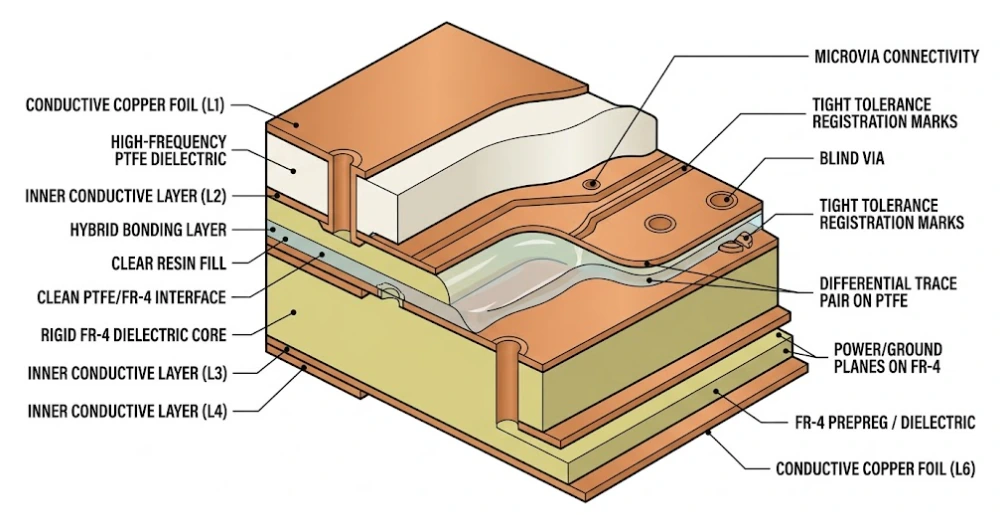

Standard lamination (a single press cycle) is sufficient for boards that only use mechanical through-hole vias. However, modern high-density designs (smartphones, AI motherboards) require blind and buried microvias to save routing space. This necessitates Sequential Lamination.

In a 2+N+2 HDI build, the factory cannot simply press everything at once. We must first laminate the inner core (the "N" layers), mechanically drill it, plate it, and etch it. We then add a layer of prepreg and copper foil to both sides, laminate the board a second time, laser drill the microvias, plate, and etch. Finally, we repeat the process for a third lamination cycle to add the outermost layers.

Every additional press cycle subjects the inner core to another massive thermal shock, causing the material to shrink slightly each time. We use highly stable, low-CTE laminates and predictive scaling compensation to ensure that the laser vias drilled during the third press cycle perfectly hit the microscopic copper capture pads buried inside the board.

3. The Complexity of Hybrid Lamination (PTFE + FR-4)

For high-frequency RF and microwave applications (e.g., 77 GHz automotive radar), engineers require ultra-low-loss materials like PTFE (Teflon) from Rogers or Taconic. However, building a 12-layer board entirely out of PTFE is prohibitively expensive. The solution is Hybrid Lamination, where the critical RF outer layers use PTFE, and the inner structural layers use inexpensive FR-4.

The Engineering Challenge: PTFE and FR-4 have drastically different Coefficients of Thermal Expansion (CTE) and melt temperatures. If pressed together using standard FR-4 prepreg, the PTFE layer may delaminate or warp wildly during cooling.

The APTPCB Solution: We deploy specialized, low-loss thermoset bonding prepregs (such as Rogers RO4450F or Taconic fastRise 27) that are chemically formulated to adhere to both PTFE and FR-4. We engineer a highly customized, dual-ramp thermal press profile that respects the curing curves of both disparate material systems, ensuring a flat, reliable hybrid board.

4. Managing Board Warpage (Bow and Twist)

A PCB must be exceptionally flat to undergo SMT assembly; excessive warpage (bow and twist) will cause the pick-and-place machine to drop components inaccurately, or cause BGA solder joints to crack open during reflow. Warpage is almost entirely driven by asymmetrical lamination stack-ups.

As a rule of physics, a board must be symmetrical across its Z-axis center. If you place a solid 2 oz copper ground plane on Layer 2, but Layer 9 (its mirror opposite) only has sparse 1 oz signal traces, the board will curl like a potato chip as it cools down from the 200°C lamination press, because the heavy copper shrinks at a different rate than the resin. Our engineering team enforces strict DFM guidelines, often recommending "copper thieving" (adding non-functional copper pour to sparse areas) to balance the metal density and ensure your boards arrive perfectly flat.