Advanced Engineering Guide

Overcoming Interconnect Challenges with Advanced Manufacturing

Designing a high-density, AI-driven, or high-power printed circuit board in modern ECAD software (like Altium Designer, Cadence Allegro, or Mentor Xpedition) is relatively straightforward in the digital realm. The true challenge arises when translating that digital model into physical reality. As a tier-1 advanced PCB manufacturer, we frequently guide our global clients through the critical intersection of electrical design intent and mechanical manufacturing physics. Below is a deep dive into the engineering guidelines we apply to ensure your advanced hardware scales reliably.

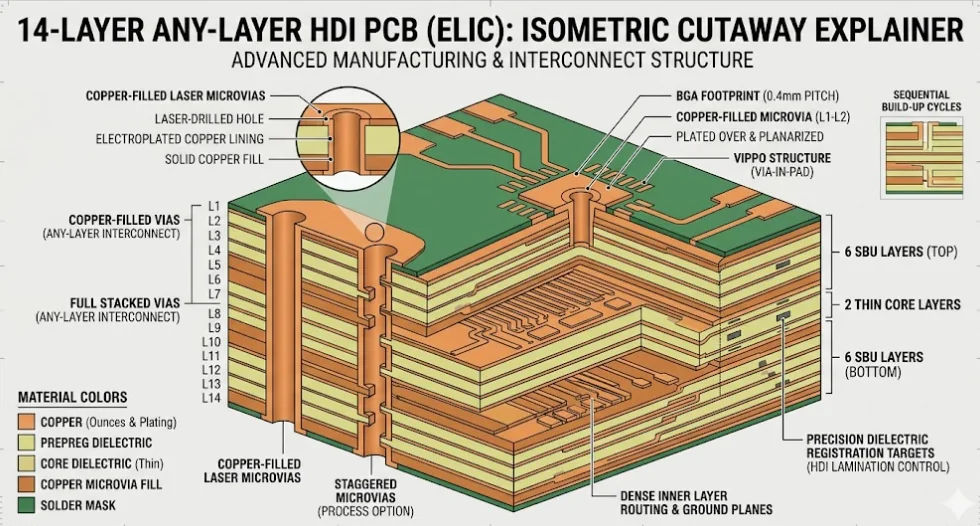

1. The Reality of High-Density Interconnects (HDI) and Microvias

When engineers transition from standard through-hole designs to HDI, the entire manufacturing paradigm shifts. HDI relies on blind and buried microvias, typically formed by highly focused UV/CO2 lasers rather than mechanical drill bits. Because a laser cannot effectively evacuate debris from deep layers without widening the hole excessively, microvias are strictly restricted to an aspect ratio (depth to diameter) of approximately 0.8:1 to 1:1.

To connect deeper layers (e.g., routing from Layer 1 to Layer 4), we must deploy Sequential Lamination. We press the inner core, laser drill, plate it with copper, and then add another layer of prepreg and copper foil before pressing the board again in high-temperature hydraulic presses. A 3+N+3 HDI board undergoes four separate, grueling lamination cycles. This introduces immense challenges in material shrinkage (scaling) and layer-to-layer registration. At APTPCB, we utilize real-time X-ray targeting and highly stable low-CTE laminates to ensure that a 3-mil laser via hits a 7-mil capture pad flawlessly, even after multiple extreme heat cycles.

2. VIPPO and Resin Filling Dynamics for Fine-Pitch BGA

Via-in-Pad Plated Over (VIPPO), also known as POFV (Plated Over Filled Via) in some regions, is mandatory for high-speed processors, FPGAs, and fine-pitch BGAs. If a via inside a pad is left unfilled, the solder paste applied during the SMT assembly process will literally wick down into the hole due to capillary action. This starves the BGA solder joint, causing fatal open circuits or mechanically weak bonds that fail under operational vibration.

Our VIPPO process utilizes specialized vacuum-plugging machines to force 100% solid epoxy into the via barrel, preventing any outgassing or "pop-corning" during the intense heat of reflow. After the epoxy is cured, precision planarization machines grind the board perfectly flat before the final copper cap is electroplated over the via. We offer both non-conductive epoxy (the industry standard, offering excellent CTE matching) and conductive silver/copper epoxy for enhanced thermal and electrical transfer.

3. Extreme Heavy Copper and Etch Compensation Physics

Power electronics, particularly in the EV automotive, solar inverter, and industrial robotics sectors, demand Heavy Copper PCBs carrying 3 oz, 4 oz, or even up to 10 oz of copper per layer. The fundamental manufacturing law here is "Etch Factor." When chemically etching thick copper straight down, the acid inevitably attacks the sidewalls laterally, creating a trapezoidal trace profile.

If you design a 5-mil space between two 4-oz traces, it is physically impossible to manufacture—the acid cannot clear the gap without over-etching and destroying the traces entirely. Our CAM engineers apply rigorous "Etch Compensation" rules. We strategically broaden your traces in the CAD data so that after the chemical undercut occurs, the final physical trace exactly matches your design intent. For heavy copper, we mandate significantly wider trace/space rules and utilize high-resin-content prepregs (like 106 or 1080 weaves) to completely fill the massive canyons between thick copper traces, preventing dielectric voids that lead to CAF (Conductive Anodic Filament) failure.

4. Signal Integrity and Controlled Impedance for 112G PAM4

Advanced manufacturing isn't just about making things small; it's about making them electrically pristine. For modern protocols like PCIe Gen5, 400G Ethernet, or 112G PAM4 SerDes channels, even a slight impedance mismatch causes signal reflections that destroy the data eye diagram. While standard boards tolerate ±10% impedance variation, advanced high-speed applications require a stringent ±5% tolerance.

We achieve this ±5% impedance mastery by combining three critical disciplines:

1. Material Homogenization: We utilize spread-glass fabrics (like 1067 or 1035) to eliminate fiber-weave skew, and HVLP (Hyper Very Low Profile) copper foils to minimize skin-effect loss at high frequencies.

2. Advanced Simulation: We use Polar Si9000 field solvers, factoring in the exact pressed thickness of the dielectric after the resin flows during lamination, rather than relying on raw datasheet numbers.

3. Empirical Verification: We place TDR (Time-Domain Reflectometry) test coupons on the waste margins of every production panel, physically measuring the impedance before the boards ever leave our factory floor.

5. Thermal Management for AI Hardware & Enterprise Servers

As AI motherboards and computing power PCBs (算力PCB) pack increasingly dense arrays of NPUs and HBM modules, thermal extraction becomes the limiting factor. FR-4 is a thermal insulator. To combat this, we implement advanced thermal management techniques. Beyond standard thermal via arrays, we offer Embedded Copper Coins (U-Coin, T-Coin, and I-Coin profiles) pressed directly into the PCB. These provide a solid metallic path from the heat-generating die directly to the chassis or liquid cold-plate, offering thermal conductivity orders of magnitude higher than standard plated vias.

6. Best Practices for Rigid-Flex Design

Rigid-flex PCBs represent the pinnacle of electro-mechanical integration. To ensure your rigid-flex design survives its intended bending cycles, always route traces perpendicular to the bend line. Avoid placing vias or plated through-holes within the flex zone or near the rigid-to-flex transition line. Finally, utilize "teardrops" where traces connect to pads on the flex layers to prevent stress fracturing. Our engineering team conducts a thorough mechanical review of your bend radii and material stack-up before any flex circuit enters production.