CAM Engineering Checklist

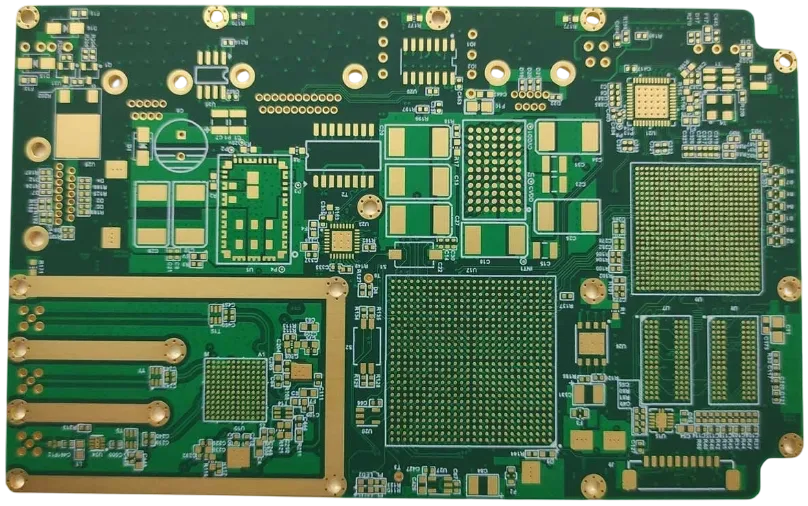

DFx‑Reviews fixieren Dielektrikumsziele, Kupferbalance und Impedanzmodelle vor der Fertigung.

- Materialien (Tg/Df) und zulässige Alternativen bestätigen.

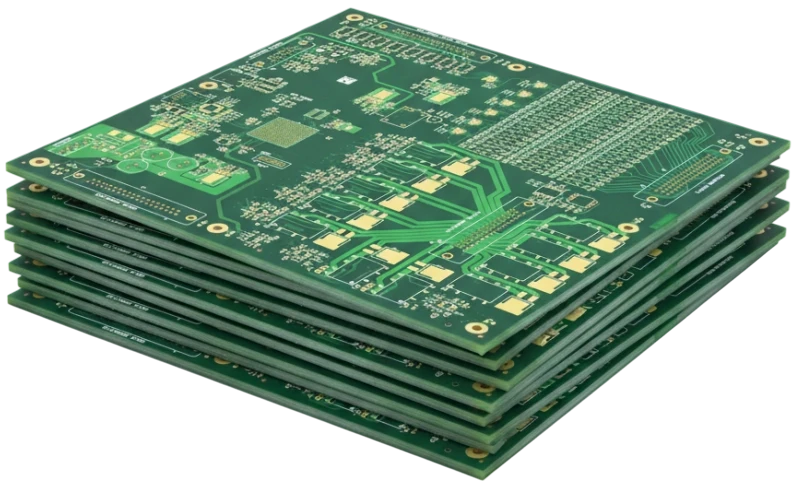

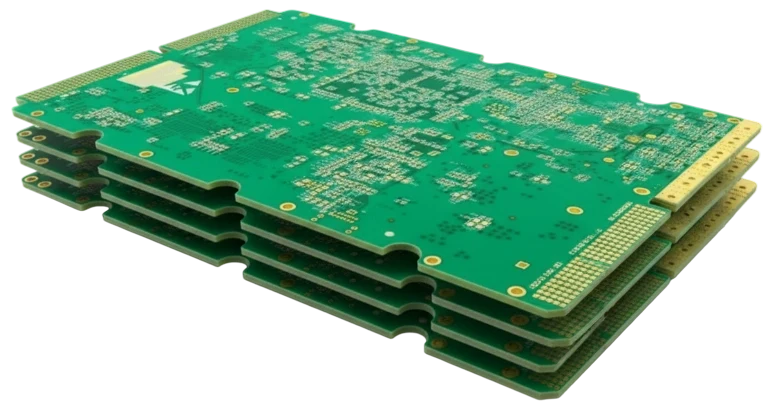

- Laminationsplan und Anforderungen an sequentielle Builds definieren.

- Impedanz modellieren und Coupon‑Referenzen aufnehmen.

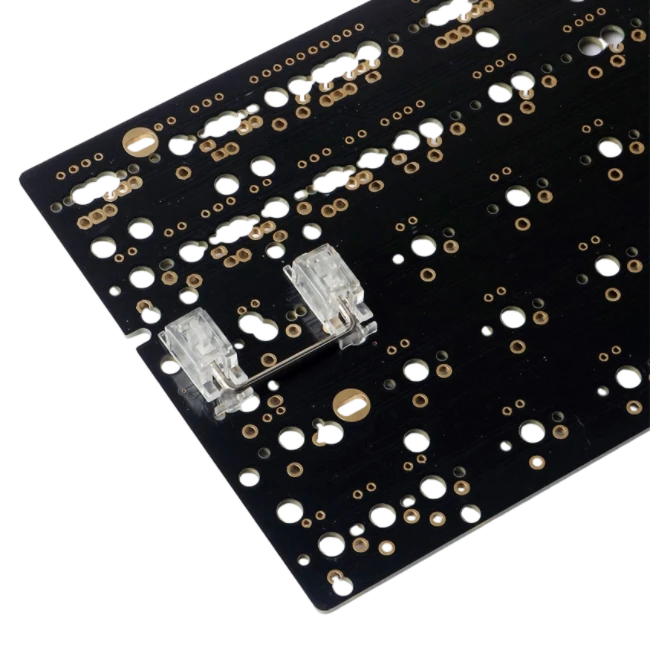

- Via‑Fill, Backdrill und Tiefenkontrolle spezifizieren, wo nötig.

- Finish, Mask und Coating‑Keep‑outs detaillieren.

- Bake-/Handling‑Anweisungen für High‑Tg‑Builds dokumentieren.