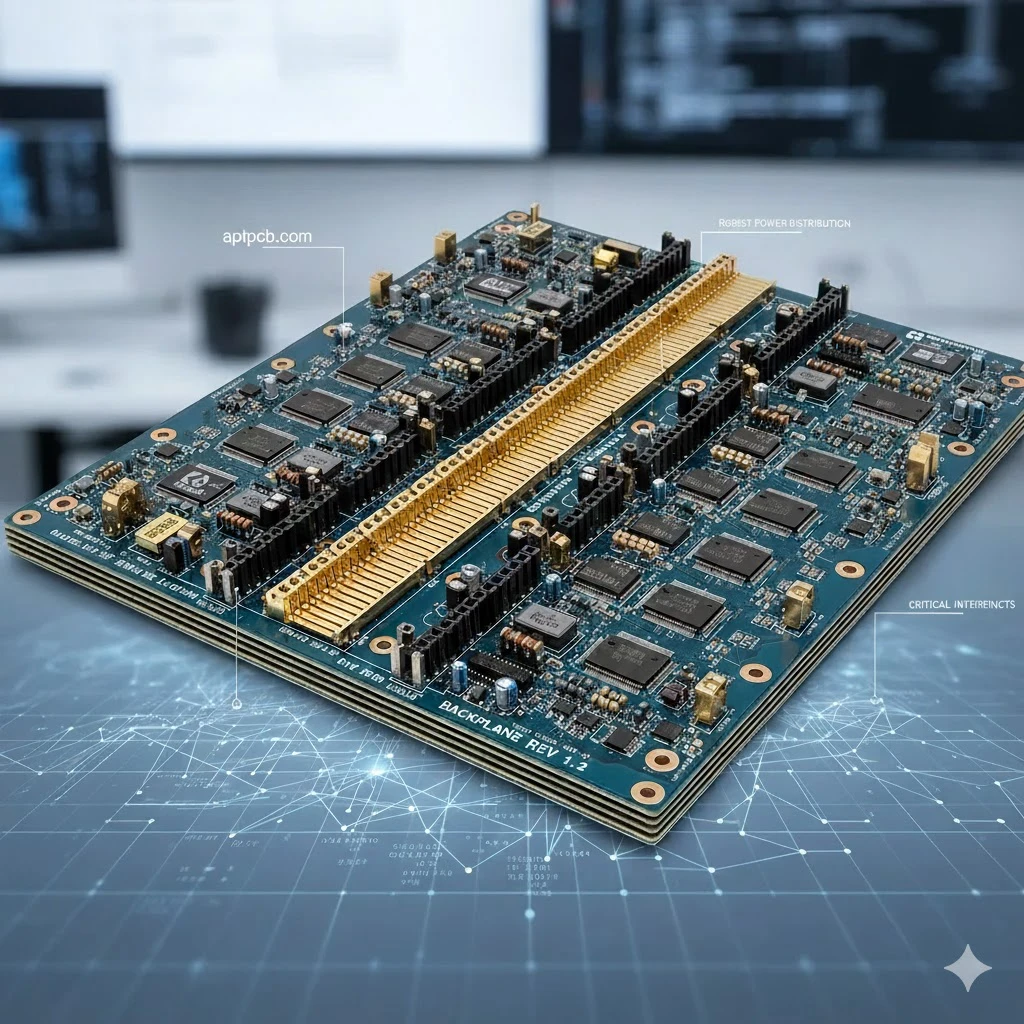

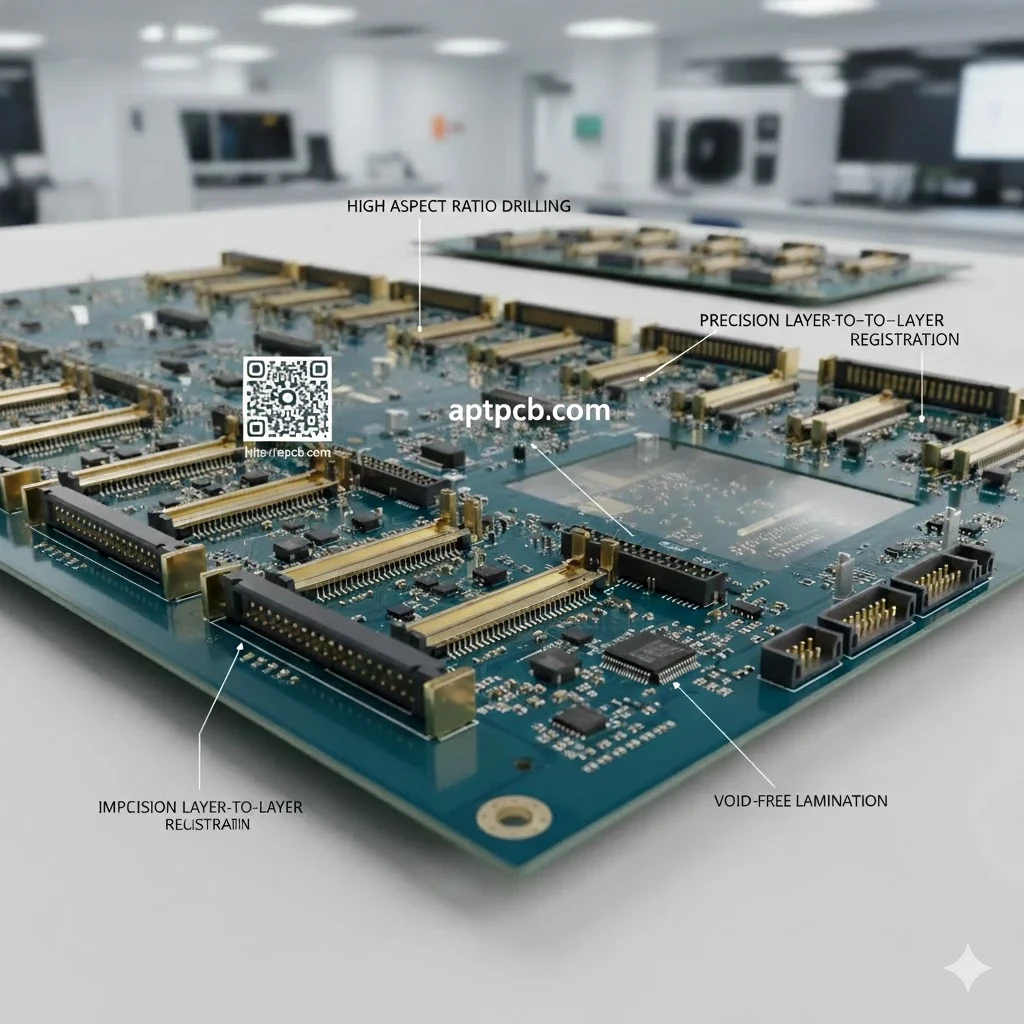

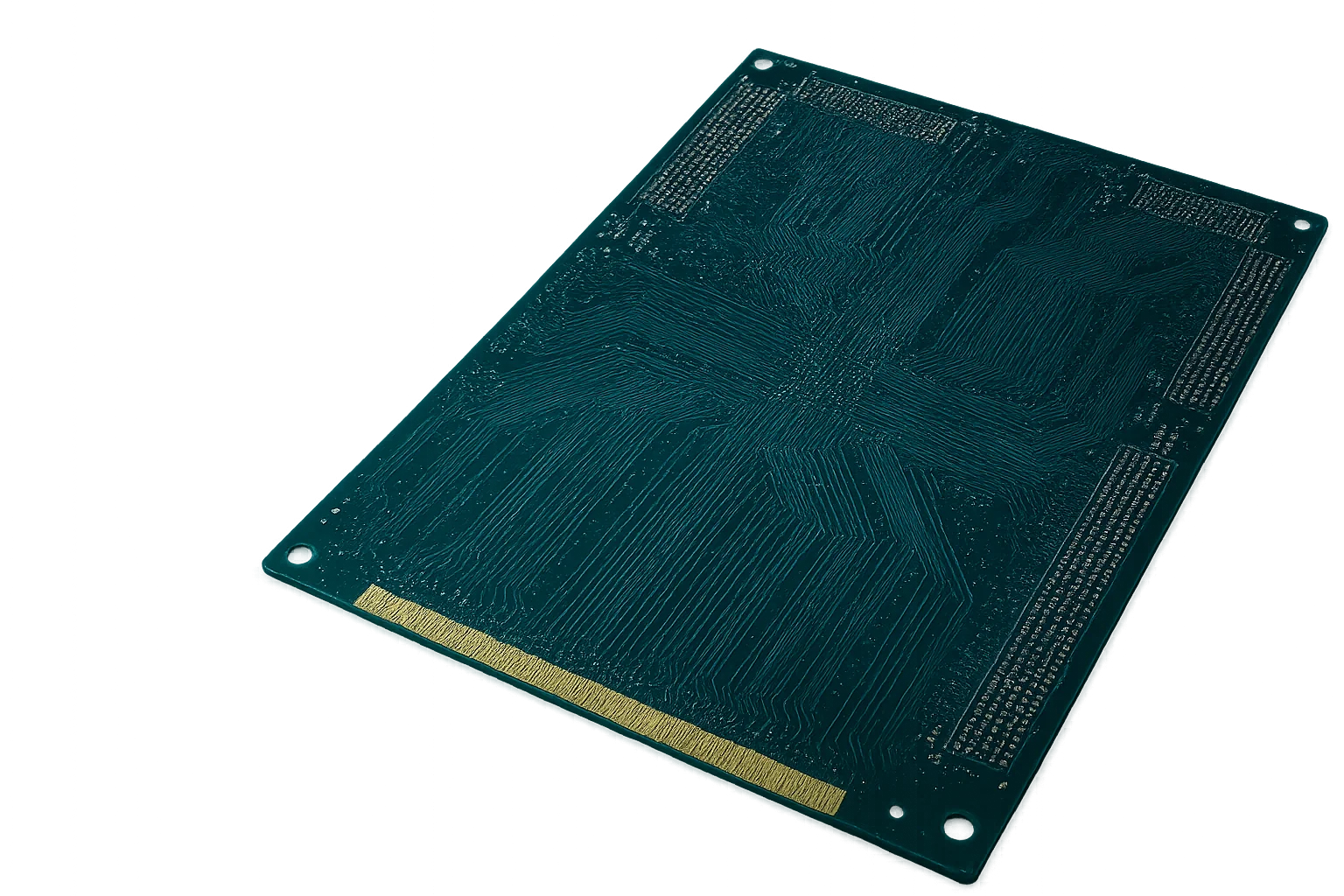

Backplane Stackup Engineering

CAM + SI teams create stackups, impedance tables, and drill/backdrill files.

- Confirm low-loss laminates and copper weights.

- Define backdrill layers and depths.

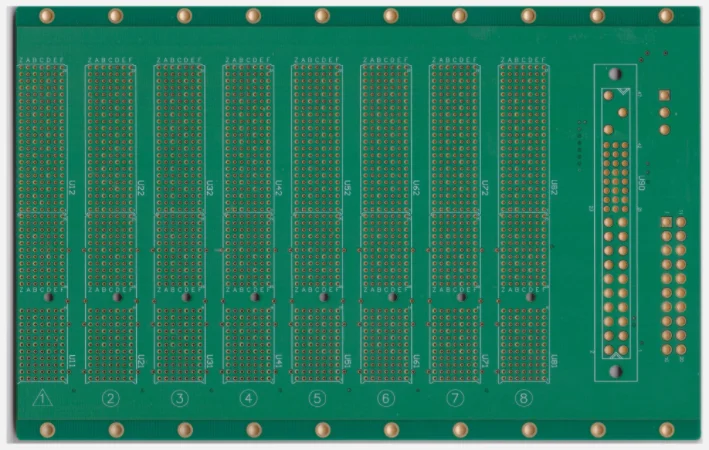

- Plan press-fit footprints and tolerances.

- Model impedance and create coupon layouts.

- Specify finish/coating keep-outs for connectors.

- Document panelization, fiducials, and handling.